### **Dual Channel 3.0 GSPS Analog-to-Digital Input Module**

#### **Features**

- 14-bit resolution

- Dual Channel 3.0 Giga samples/sec

- AC Coupled Input

- Analog Input nominal 0 dBm

- SFDR at max sample rate is >70 dB (See Figures 3,4,5)

- 3dB sample-and-hold Bandwidth 10 MHz 4.0 GHz

- External 1PPS input for precision time stamping of data

- External 10MHz reference input

- Dual I/O Site module for use with ICEPIC8

- ICEPIC8 is a PCIe 8-Lane series DSP Card

Figure 1 ICE-A2D-m20 on a PCIe 8-Lane, PIC8S(Short)

### **Applications**

- Multichannel, multimode receivers

- High Performance, Very Wideband Digital Down Conversion (DDC)

- Wideband Microwave, Wideband Radar

- Base Station CDMA, GSM, WCDMA Testing

- Direct Digital receivers

- Base station infrastructure

- Communications instrumentation

- Radar, infrared imaging

- Instrumentation, Test and Measurement

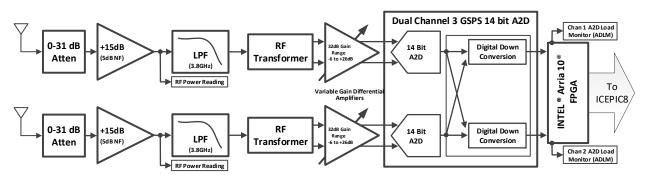

Figure 2 - Signal of Interest Flow for both channels

### **Product Description**

The ICE A2D-m20 is a dual channel 14-bit analog-to-digital converter input module for use with the PCIe Gen3 ICE-PIC8 and ICE 8<sup>th</sup> generation series of high-speed digitizer interfaces. There are two digital down converters accessible from either A2D channel. Further decimation and sub-band digital tuning of the DDC output is also available on the ICEPIC8 card. Various DDC decimation choices are available. Using the A2D-m20 on the ICEPIC8 DSP card can yield a maximum of two 500MHz Complex Integer bandwidths or one 1GHz Complex Integer bandwidth [Complex Integer (CI)] that can be processed in real-time through a single ICEPIC8 series device.

The on-board clock synthesizer uses a 10MHz reference from either an external source or via an on-board temperature-controlled crystal oscillator (TCXO).

The use of external 10 MHz and 1 PPS reference signals allows for a disciplined reference and precision time tagging/stamping of digitized data.

The RF Power Reading is a value that estimates the input at the source compensating for the attenuator value and amplifier value.

The analog-to-digital load monitor (ADLM) provides input loading to allow optimization of the attenuation and amplification of the input signal.

Page 1

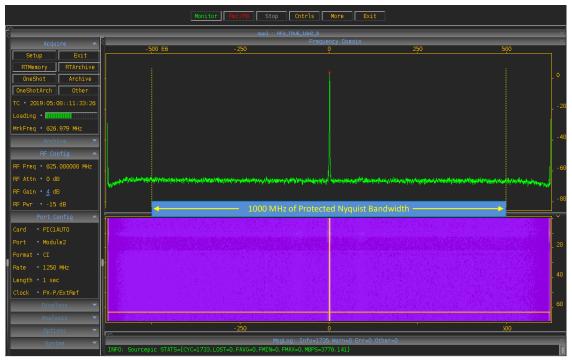

#### One Channel of 1000MHz of protected Nyquist bandwidth

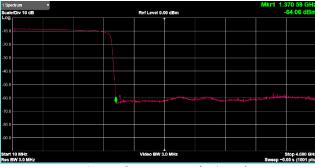

Figure 3 - Typical >70dB Spurious Free Dynamic Range (SFDR) in 1GHz of protected Nyquist bandwidth

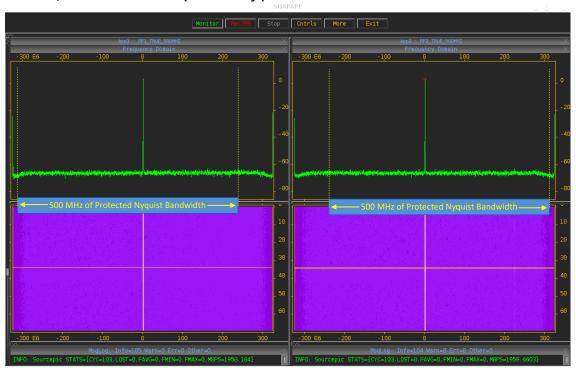

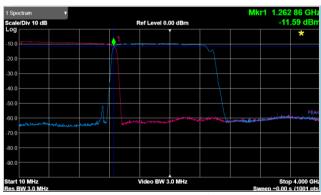

#### Two Channels, each with 500MHz of protected Nyquist bandwidth

Figure 4 - Dual Channel Typical >70 dB Spurious Free Dynamic Range (SFDR) in 500MHz of protected Nyquist bandwidth

### **Example Use Scenario**

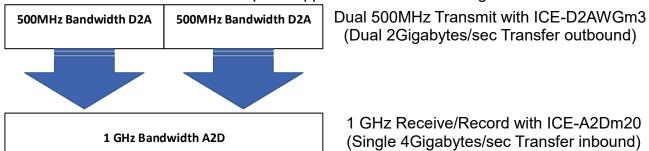

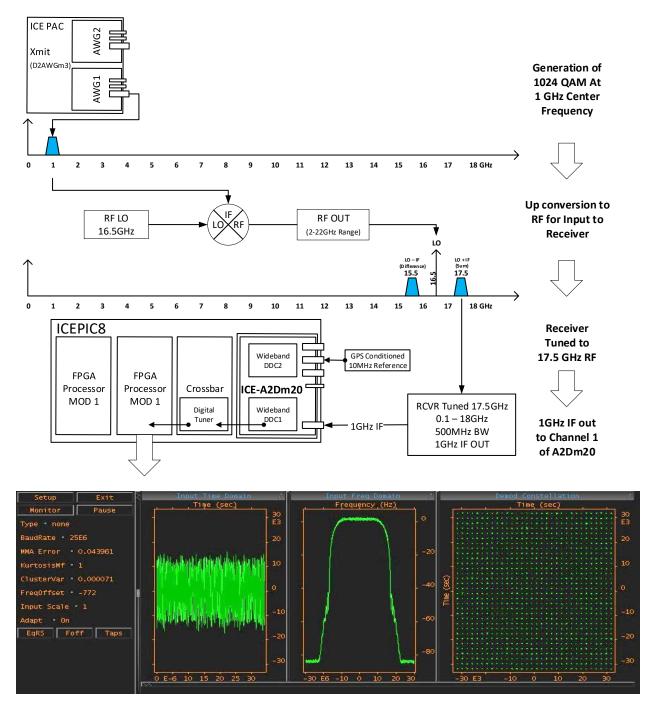

Generation and Capture Application shown in the figure 5

1 GHz Receive/Record with ICE-A2Dm20 (Single 4Gigabytes/sec Transfer inbound)

Figure 5 - PIC8 #1 with Dual D2AWGm3 Output Modules / PIC8 #2 with A2Dm20 1GHz BW Input A2D clock rates of 2500 MHz and 2600 MHz provide Nyquist protected bandwidth of 1000 MHz and 1040 MHz respectively.

#### Example of Pre-select Filtering for Nyquist Zones 1 (10-1250MHz) and 2 1250-2500MHz)

The inbound bandwidth to the A2Dm20 front-end is 10-3800 MHz. All frequencies with this range are available. The availability of all frequencies between 10 and 3800MHz occurs when a broadband antenna / amplifier combination is used as the analog input to the digitizer. There are two digital down convertors used to consume pre-detected data from the digitizer. In order to digitize and capture data, a sampling rate of 2500 Mega-samples/sec is used. When using this sampling rate, *without* pre-select filtering of the 10-3800MHZ input frequency spectrum, all spectral data from 1250MHz to 2500MHz will fold down on top of spectral data from 0-1250 MHz. All folded signals in the 1250-2500 MHz range will be inverted in frequency and mixed and inter-modulated with the 0-1250MHz signals. This is undesirable. This 1250MHz point in the frequency spectrum is referred to as the "fold point" or the [Sampling Frequency / 2, aka  $F_s/2$ ]. The range of 0-1250MHz is often referred to as Nyquist Zone 1. The range of 1250-2500MHz is referred to as Nyquist Zone 2. For this reason, pre-select filters isolating these Nyquist Zones must be used (see figures 7 and 8).

Alternatively, if the input to the A2Dm20's analog front-end is from an already filtered input, then preselect filters are unnecessary. For example: A 500MHz bandwidth receiver IF at 1.0GHz center frequency or a block down converter with 1200MHz bandwidth at 1875MHz center frequency. Occasionally a lowpass filter may be used if necessary, for spectral purity.

When using the A2Dm20 for single 1.0 GHz bandwidths a digitizing sample rate of 2500 Mega-samples/sec is used. The 1<sup>st</sup> Nyquist zone is from 10-1250 MHz for 2500MSps and 10-1500 for 3000MSps. This 1<sup>st</sup> Nyquist zone limit is simply the sampling rate divided by 2.

The front-end bandwidth to the A2Dm20 is wide band: 10-3800 MHz. To properly digitize a signal that is within the first Nyquist zone a pre-select low pass filter (LPF) must be used. This LPF rejects signals in 2<sup>nd</sup> Nyquist zone and stops them from folding down on top of the first Nyquist zone. An example of this pre-select LPF is shown in figure 7 below.

The below diagram shows a very sharp cutoff low pass filter (Figure 7) with a cutoff at 1370.59 MHz. Figure 8 shows a very sharp cut off bandpass filter (Blue Trace) for digitizing in the 2<sup>nd</sup> Nyquist zone. The sharp cut off in both figure 7 and 8 require cascading two 10 Pole, lumped element, filters. Figure 7 achieves a clear unoccupied spectrum above 1370.59 MHz at 50dB down. A digitize rate of at least twice this cutoff frequency is desirable for proper Nyquist sampling for accurate spectrum capture. The sampling rate of the A2Dm20 is called the RFRate. To maintain Nyquist, an RFRate from 2750 to 3000 is required. Alias down-conversion occurs when digitizing the 2<sup>nd</sup> Nyquist zone.

Figure 6 Low Pass Filtering of Nyquist Zone 1 (Red Trace)

Figure 7 Band Pass Filtering of Nyquist Zone 2 (Blue Trace)

#### Example of a High-QAM signal digitized/processed with the ICE-A2Dm20

The ICE-A2Dm20 Dual Channel Analog-to-Digital Input Module uses an RF Diversity Receiver architecture that accommodates DOCSIS 3.0 CMTS upstream receive paths. DOCSIS 3.0 uses 5.36 Megabaud 256QAM signaling protocol. We used a 25.0 Megabaud, 1024QAM signal for testing the ICE-A2Dm20. High QAM processing requires superior very low phase noise oscillators in the design to be able to perform demodulation with the Error Vector Magnitude (AKA Cluster Variance [ClusterVar]) shown in figure 8. We tested the ICE-A2Dm20 with a 25 Megabaud 1024 QAM signal. Figure 8 shows a real-time demodulation of the digitized signal centered at 1GHz in the 1st Nyquist zone.

Figure 8 Signal Flow and Realtime Demodulation of High QAM.

Page 5

### Input Specifications

| Parameter                              | Minimum | Typical | Maximum | Units |

|----------------------------------------|---------|---------|---------|-------|

| Analog Input (Both Channels)           |         | -10 dBm | +5 dBm  | dBm   |

| Analog 3dB Passband                    | 10.0    |         | 4000.0  | MHz   |

| External Clock Input <sup>1</sup>      | 0.5     | 1.0     | 2.0     | V p-p |

| External Ref <sup>1</sup> (AC coupled) | 0.5     | 1.0     | 2.0     | V p-p |

| Analog Input Impedance (AC Coupled)    |         | 50      |         | Ohm   |

| Sample Clock Range                     | 2.500   |         | 3.000   | GHz   |

|                                        |         |         |         |       |

Table 1 Note 1: Operation using external reference of 10MHz replaces the external clock input. Sample clock is then generated from the 10MHz reference.

### **Absolute Maximum Ratings**

| Parameter                                                                                    | Value                                            | Units                                                                        | Conditions                                                                                          |

|----------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Electrical Analog Input Maximum² AVcc DVcc PPS input External clock input Analog input power | +10.0<br>2.0<br>2.0<br>0 to 3.3<br>0 to 2<br>+10 | dBm<br>VDC<br>VDC<br>Vpeak into 50ohm<br>V p-p into 50ohm<br>dBm (50ohm ref) | dBm Max Before Damage<br>VDC Max Before Damage<br>VDC<br>TTL 3.3V Expected 50ohm<br>dBm (50ohm ref) |

| Environmental<br>Operating Temp<br>Storage Temp                                              | -10 to +65<br>-40 to +85                         | Degrees C<br>Degrees C                                                       |                                                                                                     |

Table 2

Note 2: It is recommended that if inputs greater than +5 dBm are expected a limiter be used.

Analog Input Maximum is 2.0 Volts which is equivalent to +10dBm.

Warning: Operation of this module beyond any of these parameters (temperature, voltage, and input power) may cause permanent damage. Exposure to absolute maximum ratings for extended periods may affect module reliability. Operation of the module beyond these specified parameters voids the factory warranty.

### **Connectors**

| Connector                                                                                                                                                          | Manufacturer                                           | Part Number                                                                     | Description                                                                                                                                | J-Number                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| Signal Connections Analog In 1 Analog In 2 Clock or Reference In 1 Pulse Per Second (PPS) In Board Connection Data Connection Power Connection Physical Connection | Digi-Key<br>Digi-Key<br>Digi-Key<br>Digi-Key<br>Samtec | 142-0701-871<br>142-0701-871<br>142-0701-871<br>142-0701-871<br>QTE-020-03-F-DA | Edge Mount SMA Connector Edge Mount SMA Connector Edge Mount SMA Connector Edge Mount SMA Connector 40 Pin Connector Standard 2-pin Header | J2<br>J5<br>J7<br>J8<br>J3, J6<br>J1, J4 |

| Standoff (2 each)  Mating Connectors  SMB (J1, J4)  Data (J3, J6)                                                                                                  | Amp<br>Samtec                                          | # 1-5414946-1<br>QSE-020-01-F-D-A                                               | Physical Connection  40 Pin Connector                                                                                                      | J3, J6 Mate                              |

Table 3

#### **ICE Interface Cables**

Rigid, formable, Tensolite high performance RF cable is recommended for best signal quality. For SMA mating cables we recommend SMA cables with proper frequency response to at least 4 GHz for operation at the ADC's full "sample and hold" bandwidth.